by Author Author

Submission date: 21-Jul-2020 05:11PM (UTC+0530) Submission ID: 1360363499 File name: 6.docx (428.35K) Word count: 5597 Character count: 27229

## Background 1 2 Hearing loss is a debilitating factor for communication breakdown and associated with social 3 isolation. One of the rehabilitative approaches to alleviating hearing loss is hearing aid. With 4 the advancement and proliferation in digital technology, most of its concepts applied in various domain are imbibed and utilized in the fabrication of hearing aid. The budding 5 6 professionals must have minimal understanding of the working principle of digital hearing 7 aids is an essential part of the knowledge required to troubleshoot the aid. This will help for those who intend to keep up with the knowledge of the digital technology in hearing aid that 8 9 will inevitably continue. In this mini-review paper, we are presenting the architect of digital 10 hearing aid, the working principle of each component and its limitation are explained with 11 substantial literature review. 12 The architecture of Digital Hearing Aid 13 14 The primary architect of digital hearing aid comprised of arithmetic operations such as ADD, SUBTRACT, MULTIPLY, etc. and logical operation such as AND, OR, NOT, 15 16 XOR, etc. (Stetzler et al., 2008). The architecture also includes on-chip registers to store immediate results, memories to store signal samples (RAM), and memories to store filter 17 coefficients (ROM). To amplify the discrete version of the signal from the output of the 18 microphone needs multiplication operation. To illustrate, suppose the microphone of the 19 hearing aid picks the signal having 2 volts at one data point, then it converts into binary i.e 20 010. These binary digits are fed to the digital circuitry to amplify the signal. To be specific, 21 the binary value 010 is multiplied using impulse response, having the characteristics of filter 22 coefficients, which has the application of amplification 10 (2). The resulting binary value 100, 23 24 where it accounts for 4 volts (refer convolution section for detailed explanation). Similarly, a series of binary values corresponding to the data point is processed. 25

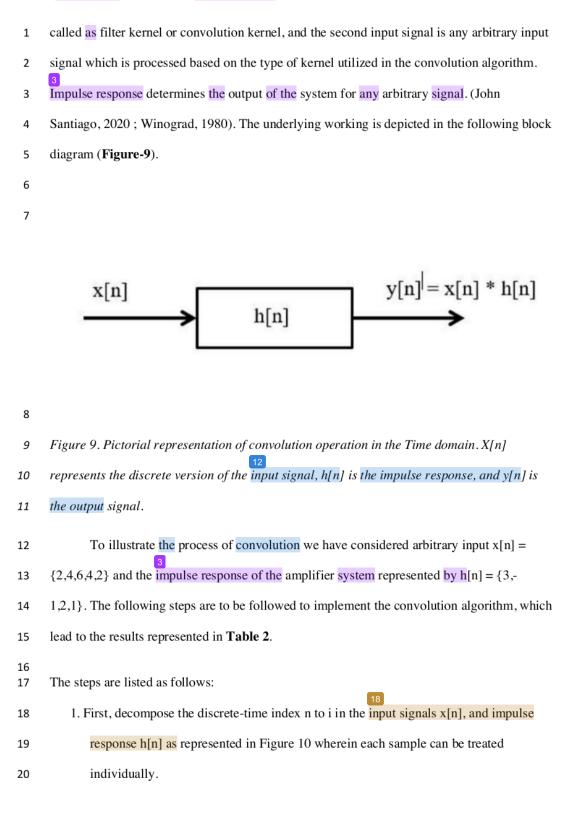

| 1  | To purport, any digital circuit in the hearing aid should fetch (n) binary values from            |

|----|---------------------------------------------------------------------------------------------------|

| 2  | memory corresponding to the input signal plus the program instruction describing what to do       |

| 3  | with the data to yield accurate results. This digital operation requires a power supply. Stetzler |

| 4  | et al., (2008) have developed a digital hearing aid that consumes less power and has              |

| 5  | thoroughly thrown light on the architecture of the developed hearing aid. The programmable        |

| 6  | devices are offering more sophisticated algorithms that consume less. Whereas in the analog       |

| 7  | hearing aid, the components used such as resistors, capacitors, inductors, and transistors are    |

| 8  | sensitive to environmental changes and subsequent aging deteriorates accuracy of operation.       |

| 9  | (Philippe et al., 2020)                                                                           |

| 10 |                                                                                                   |

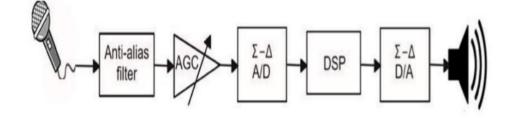

| 11 | The Digital Signal Processing illustrated (in Figure 1) allows the implementation of              |

| 12 | sophisticated and complex algorithms in real-time on a Very Large Scale Integrated Chip           |

| 13 | (VLSI). The VLSI reduces the cost and DSP operations can be easily employed in the digital        |

| 14 | hearing aid. It can easily be modified in real-time, often by changing in simple programming      |

| 15 | and or by the reloading of registers in DSP. The same functions may be implemented using          |

| 16 | hardware, which will pave the way for increasing the speed of the execution, but the circuit      |

| 17 | complexity will also increase considerably.                                                       |

18

19

20 Figure 1. Simplified Block diagram of the architecture of digital hearing aid

| 1  | A microphone should have the characteristics of a reduced noise floor that transduces                           |

|----|-----------------------------------------------------------------------------------------------------------------|

| 2  | the input speech sounds into an electrical representation of acoustic sounds. The electrical                    |

| 3  | <sup>9</sup><br>signal is passed through a low pass anti-aliasing filter. The audible frequency range for which |

| 4  | the human ear responds is 20Hz to 20 kHz, and thereby it is required to remove the frequency                    |

| 5  | content of the input signal beyond 20 kHz. To employ this task, the anti-alias filter that is                   |

| 6  | nothing but low pass filter with cutoff frequency of 20 kHz is employed before the signal                       |

| 7  | transformed to digital signal making use of the A to D converter. This process will remove                      |

| 8  | high-frequency components, thereby preventing aliasing effect, which otherwise increases                        |

| 9  | noise and interference at the output. The resultant output is amplified using an automatic                      |

| 10 | volume control amplifier as the transduced voltage of the input signal picked up by the                         |

| 11 | microphone is too weak. This automatic volume control amplifier is a preamplifier that will                     |

| 12 | increase the mic-level signal to line level signal to support the process of treating the signal in             |

| 13 | the digital domain after converting the analog signal to a digital signal.                                      |

14

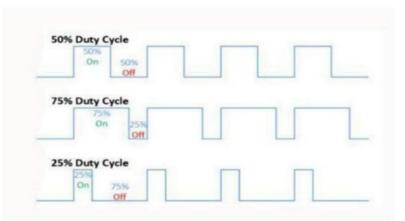

Automatic gain control employs class D amplifier, where the signals are encoded into 15 16 the duty cycle of the rectangular pulses, which is called pulse width modulation. A high-17 intensity signal is represented by a high duty cycle, and a low-intensity signal is represented 18 by a low duty cycle. Figure 2 illustrates the resulting Pulse Width Modulated (PWM) output 19 waveform due to the dynamic nature of the signal, where its intensity varies as a function of time. For example, assume maximum voltage handled by the AGC circuit is 9 volts, and in 20 21 the following figure, the voltage appears across the circuit for half of the time, which is represented by 50% Duty Cycle. So we can say that effectively it is representing 4.5 volts of 22 the input signal. In the same way, 75% of the Duty cycle represents 6.75 volts of the input 23 24 signal, and 25% Duty Cycle represents 2.25 volts.

1

*Figure 2.* Waveform depicting pulse width modulation depicting the variation of input signal

magnitude

4 The pulse width modulated signal or the rectangular signal is amplified, and then a 5 lowpass filtered, which results in a higher-power version of the original analog signal. Denhardt, (1966) has reported that the utility of Class D amplifiers is increasing due to 6 improvements in higher efficiency in terms of saving power, increased power density, and 7 8 better audio performance. The output of the Class D amplification employed in the preamplifier is converted from analog signal to digital signal using a sigma-delta analog to 9 10 digital converter. The operation of sigma-delta modulation is explained in the later section. 11 Once the data is converted to the digital domain, the DSP processes the digital stream using the various algorithms like noise reduction algorithm, frequency shaping algorithm, etc. using 12 a convolution algorithm that makes use of impulse responses. The convolution process using 13 impulse response of the appropriate system could be of filters, equalizers, etc. will help to 14 enhance the speech input. A y [n] represents the output signal obtained from convolving the 15 impulse response (h [n]), with the discrete version of the input signal (x[n]). The desired 16 17 output is stored in memory. Besides, the output stored may further be modified in terms of 18 increasing the gain as a function of frequency using audio processing algorithms. The sigma-

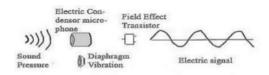

delta digital to analog converter transforms the digitally processed data back to an electrical 1 signal, which is presented to the real world through the end stage transducer i.e receiver. The 2 detailed description of it is explained in the later section. The electrical signal is converted 3 4 into an acoustic signal in the end-stage transducer. 5 6 Input transducer in the hearing aid. The first and foremost component in the 7 hearing aid is the microphone, which is also called the input transducer converts sound energy into electrical signals. Electret condenser microphone (ECM) technology is most 8 9 extensively used in all types of hearing aids, whether it could be an analog hearing aid or 10 digital hearing. Electret condenser microphone use fluorocarbon foils as the electret, has uniform frequency response and less variation in sensitivity over temperature (Chakraborty et 11 at, 1975) 12

13

14 *"Figure 3.* Working principle of the electret condenser microphone

One of the plates of the capacitor act as diaphragm vibrates in response to the changes in the air pressure falling on the diaphragm. This results in corresponding variations to the distance between the two plates, that is, the diaphragm and the back plate of the capacitor. This leads to variations in the voltage maintained between the two plates, which is further amplified by using a field-effect transistor. The working principle of electric condenser microphone (ECM) is described in **Figure 3**. The output voltage of the transducer needs to be amplified for improving communication and to decrease the listening effort among the

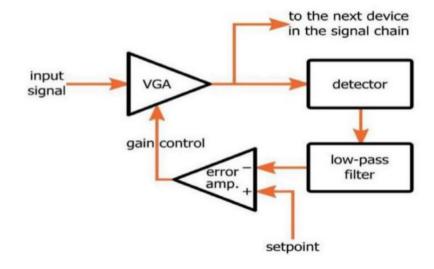

hearing-impaired population. The technology used to achieve amplification could be either 1 2 analog or digital. Automatic gain control is a circuit that controls an amplifier's gain in accordance with the instantaneous strength of the input signal picked up by the microphone to 3 4 maintain a constant output level after amplification. Automatic gain control plays the role of 5 the preamplifier, which is a flexible system in terms of adjusting the gain. This is because the input signal varies above the threshold of AGC in the hearing aids. The adjustment in the 6 7 gain is a process where the output signal of the AGC is fed back, creating a loop between input and output. This loop will make a way to compare the instantaneous value of the 8 amplitude of the output signal with the set point of error amplifier indicated in figure 4. The 9 output of the error amplifier control the gain of the amplifier in accordance with the feedback 10 signal .If the AGC circuit is installed in the hearing aid, a sufficient amplification is assigned 11 either by reducing or increasing the volume automatically relative to the signal strength. 12

- 13

- 14

15

16 Figure 4. The underlying architecture for an AGC system

| 1  | The voltage-controlled preamplifier or variable gain preamplifier should be used to step up         |

|----|-----------------------------------------------------------------------------------------------------|

| 2  | the low voltage signal picked up by the microphone. Voltage controller detect the speech            |

| 3  | signal and apply a sufficient gain depending on the applied feedback voltage and it is denoted      |

| 4  | as control signal (CV). The resultant output voltage of the envelope detector is proportional       |

| 5  | to the magnitude of the instantaneous input voltage acquired from voltage gain amplifier            |

| 6  | (VGA). It is assumed that sufficient low pass filtering is applied at its output to reject ripples. |

| 7  | The output voltage of the detector is proportional to the envelope of the amplitude of the          |

| 8  | input signal. In other words, the output voltage of the envelope detector is equivalent to the      |

| 9  | magnitude of the input voltage. The detector's output is compared against a set point               |

| 10 | (Figure-4) voltage to produce an error signal, which is then integrated to produce a voltage        |

| 11 | regulated by the gain controller. The control signal is applied to control input of the VGA,        |

| 12 | which varies the gain depending upon the applied control signal. This control signal is             |

| 13 | generated based on the difference between the reference signal in the set point and the input       |

| 14 | signal. If the error voltage is less than the reference voltage, the gain will be increased in      |

| 15 | VGA to the required voltage for further processing. This technique is usually used in union         |

| 16 | with feedback loops, leading to their self-correcting mechanism (Keim, 2016)                        |

| 17 |                                                                                                     |

| 18 | Analog to digital conversion (ADC). Analog signals are converted into a digital                     |

| 19 | signal. The analog signal has to undergo sampling, quantization, and coding for the                 |

| 20 | conversion process. The different conversion techniques use these processes.                        |

| 21 |                                                                                                     |

| 22 | Successive approximation ADC. The signal picked up by the microphone is                             |

| 23 | processed digitally using successive approximation method of ADC. The electrical                    |

| 24 | representation of the speech signal, that is, the transduced output voltage of the microphone is    |

| 25 | fed into the preamplifier to amplify the signal for further processing. This electrical signal      |

|    |                                                                                                     |

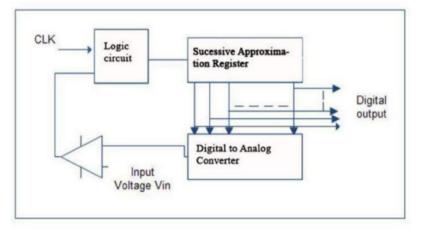

- 1 converted into a discrete signal using an analog to a digital signal converter. The working of

- 2 two architectures predominately used in the hearing aid, namely the Successive

- 3 Approximation register ADC and Sigma-Delta ADC, are explained.

4

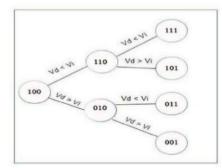

5 *Figure 5*. Block schematic representation of successive approximation ADC.

6 The architecture of successive approximation registor ADC is shown in Figure 5. To 7 simplify the illustration, we have considered the 3 bit SAR ADC. The cycle of conversion 8 starts by setting the most significant bit (MSB) of successive approximation registor to 9 '100'. This intermittent digital output (V<sub>d</sub>) is converted to an equivalent analog voltage by 10 digital to analog converter and is compared with input sampled voltage (V<sub>i</sub>) by making use of 11 comparator, as shown in the block diagram.

This comparison provides an indication by generating a high or low clock pulse through the logic circuit based on the result of the comparison carried out between V<sub>d</sub> and V<sub>i</sub>. If the result obtained is positive after the process of comparison, it gives an indication that the input sample value is high, enabling the SAR to set the next bit from MSB, which will give rise to binary value '110'. In the same line if the result obtained is negative after the process of comparison, it gives an indication that the input sample value is low lead the SAR to reset

- 1 the last set bit and to move on to next bit by setting it high giving rise to binary value '010'.

- 2 which is. The process continues until digital equivalent of analog input signal value reach the

- 3 LSB or whichever earlier. The process of conversion can be easily perceived, referring to the

- 4 flowchart depicted in Figure 6.

5

7 *Figure 6* The Flow Chart of successive approximation ADC.

8 SAR ADCs are known for consuming less power and giving accurate high-resolution 9 output. The foremost limitation of the SAR architecture is that it works with the lower 10 sampling rates and requires an extra circuitry consist of the DAC and the comparator. The 11 complexity involved in designing of SAR ADC is more expensive and relatively takes more 12 time than other ADCs to get the resultant output.

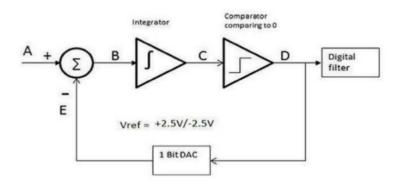

13 Delta-sigma (DS) analog-to-digital converters (ADCs). The sigma-delta converter 14 makes use of a higher sampling rate, which can also be expressed as N times the Nyquist rate 15 leading to an increase in the sampling rate much greater than sampling frequency. DS ADC 16 converts the analog signal to digital signal with one-bit resolution. Figure 7 shows the 17 architecture of the sigma-delta ADC. The output signal of the pre-amplifier which acts as an 18 input to DS ADC and is algebraically added (A-E) from the feedback signal fed to into a 19 summing node. The resulting output signal from the summing node is fed to an integrator

<sup>6</sup>

- 1 (B), and the output of the comparator (C) depends on the integrator's output. The reference

- 2 voltage is set to -2.5 if the comparator output voltage is negative and vice versa.

#### 3

#### 4

5 *Figure* 7. Block diagram of the sigma-delta modulator.

6

7 The working can be effectively understood with the following illustration (**Table -1**), the 8 input voltage to the converter from the preamplifier of the hearing aid is 1 V, and the Digital 9 to Analog Converters Voltage Refs are  $\pm 2.5$  V ( $\pm 2.5$  = High (H); -2.5 = Low (L)). The full-10 scale measure of sigma Delta ADC is 5 V (i.e. 2.5 - (-2.5)). Initially, the summing node and integrator voltage are set to 1. If the input voltage of 1 V is fed into summing node, where the 11 reference voltage of 2.5 is subtracted from the input voltage results to -1.5 V. The output of 12 summing node is algebraically summed with the initial setting of integrator voltage of 1 V. 13 The resultant voltage in the integrator is -0.5 V where it compares with the digital reference 14 in the comparator. Since the output is in negative voltage, the DAC is set at low, that is -2.5. 15 In the successive cycle, the value of DAC (-2.5 V) is subtracted with the input voltage in the 16 summing node. The resultant output is 3.5 V, which is algebraically added with the previous 17 voltage in the integrator (-0.5 V) results to 3 V. If the voltage in the integrator is positive, the 18 19 digital reference turns out to be high (that is + 2.5 V). Likewise, the process iterates until we

| 1        | get the digital output closer to the input voltage. In the table, we can see that there are six                                                                                               |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2        | times digital reference set to high (+2.5) and two times set to low (-2.5). Averaging the                                                                                                     |

| 3        | number of times, the digital reference has set to high by the total number of iteration should                                                                                                |

| 4        | closely match the input voltage $(6/8 = 0.75)$ if the iteration is more, than obviously, the digital                                                                                          |

| 5        | output will be precise to the input voltage. The high is considered as 1 in binary digit and low                                                                                              |

| 6        | as 0 in the binary digit. In this illustration, 1 volt of input is coded as HLHHHLHH or                                                                                                       |

| 7        | 10111011.                                                                                                                                                                                     |

| 8        | Here Table-1                                                                                                                                                                                  |

| 9        | The output of the difference amplifier equals the input plus the quantization noise.                                                                                                          |

| 10       | By algebraically summing the error voltage with the input signal, the accuracy of conversion                                                                                                  |

| 11       | is increased by reducing the quantization noise. The integrator performs low-pass filter action                                                                                               |

| 12       | on to the input signal and a high-pass filter action to the quantization noise leading to push                                                                                                |

| 13       | the quantization noise to higher frequencies, as shown in <b>Figure 8a. Figure 8b and 8c</b>                                                                                                  |

| 14       | determine the sampling frequency. The above process will lessen the quantization noise in the                                                                                                 |

| 15       | Sigma Delta ADC.                                                                                                                                                                              |

| 16       |                                                                                                                                                                                               |

| 17       | Conversely, if this process is not employed then the quantization noise is uniformly                                                                                                          |

| 18       | distributed over the entire frequency band distorting the frequency of interest. Nevertheless,                                                                                                |

| 19       | in the sigma-delta ADC, the distortion is kept to a minimum as the negative feedback loop                                                                                                     |

| 20       | minimizes the quantization noise making the integrator to shape noise distribution such that                                                                                                  |

| 21       | 20                                                                                                                                                                                            |

|          | the quantization noise is decreased in the low-frequency band and increased in the high-                                                                                                      |

| 22       | the quantization noise is decreased in the low-frequency band and increased in the high-<br>frequency band. This process is called <b>noise shaping.</b> The function of the comparator is to |

| 22<br>23 | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                         |

|          | frequency band. This process is called <b>noise shaping.</b> The function of the comparator is to                                                                                             |

Table 1. The feedback loop feeds back this reference voltage to the summing node where the 1 2 reference voltage is algebraically added with the input signal again. These feedback cycles bring the DAC's output to be the average of the input signal. 3 4 Suppose if the signal has the highest frequency of 8 kHz, then sampling frequency 5 6 should be twice the highest frequency, that is, the sampling frequency should be at least 16 7 kHz to avoid aliasing. In such a case, the quantized noise will be accumulated in the signal of 8 interest (Figure-8a) (Loloee, 2020; Rietjens et al., 2011). To reduce the quantization error, it 9 is ideal to increase the sampling rate and the number of bits  $(2^n)$  such that the sampled point 10 is mapped to the nearest quantization level such that quantization error referred as noise reduces after low pass filtering (Figure-8b). The oversampling frequency utilized in the 11 12 SDM eliminates the noise. The error in the signal (A-E) is partial out in the summing node. 13 The output from the summing node is algebraically summed in the integrator results in the 14 reduction of noise as a function of successive iterations. In SDM, the integrator acts as a low 15 pass filter, and this process is called noise shaping (Figure 8c). The decimator in the sigma-16 delta demodulator reduces the sampling frequency for subsequent ease of processing of digits 17 to convert back into the analog signal. 18 19 20 21 22 23

3 *Figure 8*. The technique of oversampling with an analysis in the frequency domain.

4

1

2

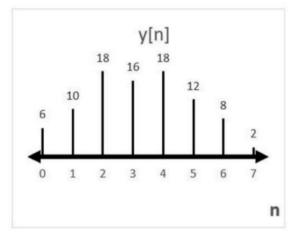

5 **Processing of digitized signal.** Once the signal is digitalized in the ADC circuit, the output is processed using impulse response. One of the digital signal processing techniques 6 used is convolution, which is a mathematical operation of two functions, where the input 7 8 digitalized signal x[n] is modified according to the function h[n], thereby the desired digitized 9 output is emanated y[n]. Convolution operation can be carried out in time domain as well as in the frequency domain. The following discussion explains convolution in the time domain 10 Convolution method of the impulse response. Convolution is the digital signal 11 12 processing technique wherein the two signals are combined using a mathematical technique or convolution algorithm, which involves multiplication and addition. Convolution is a 13 fundamental and vital concept in signal processing and analysis and it is represented by the 14 asterisk symbol (\*). To carry out the process of convolution, we require two signals as input 15 to yield the third signal, which can be treated as the digitally processed output signal. Among 16 the two input signals, the first signal is the impulse response of the system, which is also 17

- 1 2. The input signals x[i] is flipped left for the right to obtain x[-i] as represented in

- 2 Figure 3.

- 3 3. Shift the input signal by x[n-i] to get each output index n

- 4 4. The convolution x[n]\*h[n] is performed and y[n] is computed by synthesizing the

- values of x[n-i]\*h[i] as i ranges over the set of integers.

## Here Table-2

7 8

5

6

Figure 10. A. Discrete-time index n to i in the signals x[n] and h[n] and B-C represents the

8

9 iteration of the convolution process.

The illustration of convolution method is explained in Figure-8. Now we flip x[i] in order to obtain x[-i]. For n = 0, there will be no shift x[0-i] = x[-i]. For n = 0, the of product x[n-i]\*h[i] is determined and then added up to get the discrete y[0]. To illiterate [h[0] =3\*x[0]=2 then the y[0] =6; h[-1]=0\*x[-1]=4 then the y[0] =0; h[-2]=0\*x[-2]=6 then the y[0]=0, then the product of all iteration should be added to obtain  $\sum y[0]$  i.e., 6+0+0 = 6]. For n = 1, there will be right shift of x[1-i] by 1 unit, then the product of x[1-i]\*h[i] are added up to obtain y[1]. Likewise, the above process is repeated for n corresponding to 2,3 4,5,6 and 7

1 to obtain y[n], which is the resultant amplified version of the arbitrary input signal (Figure-

## 2 11).

#### 3

4

5 *Figure 11*. Pictorial representation of y[n] obtained after convolution as per the data

6 considered in our illustration

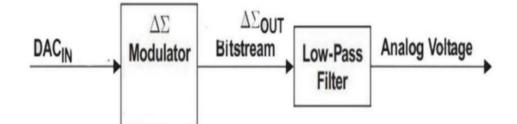

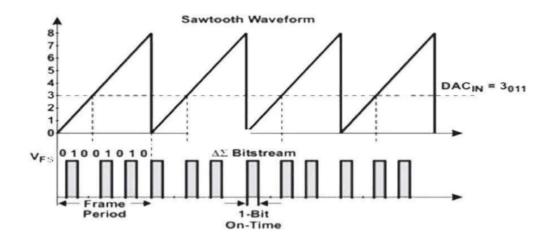

7 Restoring the processed digitized data back to analog. The output of Delta sigma  $(\Delta \Sigma)$  DAC is represented as an assembly of pulses, which can also be called as bitstream. 8 These pulses are allowed to pass through a low-pass filter to remove the noise inserted during 9 10 the conversion process, which increases the precision of the analog output voltage, as depicted in Figure 12. The resolution of a DAC determines the minute change in the analog 11 12 voltage (that is the minimum change in the analog voltage that causes the output of the DAC 13 to change ) specified by the number of input bits or input width, The Full-scale (Fs) determines the output span which represents the output when all the input bits are assigned 14 ones subtracted from the output when all the input bits are assigned to zeroes. Full-scale is 15 represented by the number of voltage levels (2<sup>N</sup> for an N-bit DAC) that can be produced by 16 the Digital to Analog Converter. A DAC is employed to signify the voltages from zero volts 17 to the maximum power-supply voltage, V<sub>CC</sub>. The lowest DAC input code should depict 0 V, 18

1 and the highest input code should depict V<sub>CC</sub>, which represents the full-scale voltage. Each

- 2 input analog voltage stage of an N-bit Digital to Analog converter is given by (Cheung et al.,

- 3 2005)

4 V<sub>LSB</sub>=

$$\frac{F_S}{2N}$$

5

6

7 Figure 12. Block diagram of Sigma Delta DAC

8 The analog output of the filter is an analog voltage, which is equivalent to the average 9 of the on-time of the pulses fed to the input to the low-pass filter. The frame period has to be 1 10 distributed into 2<sup>N</sup> parts. The on-time is characterized as one within the stream of bits in the

11 frame. The analog voltage is given by the formula mentioned below.

$$\frac{On - time}{2^N} \times \frac{1}{FS}$$

13

12

14 For example, in Figure 13, explains the DAC for the average analog output equals to  $3/8 \times$

15 V<sub>CC</sub>.

16

1 Figure 13. Bit stream output of Sigma Delta DAC for D<sub>IN</sub>3011

In this process, the output is a pool of pulses of equal width such that the average 2 3 density of the pulses corresponds to the digital input value. These pulses or the output stream 4 representing the digital output is fed through a low-pass filter to produce equivalent analog voltage. The  $\Delta\Sigma$  operation is explained with a 3-bit example in Table -3. Let us consider Fs 5 6 =6 V, 8-bit stream in a frame and number of on-time pulses within the frame is 4 (10101010) 7 then the output voltage delivered is 5.3 V. Table 3 shows the stream of bits representing the inputs of a 3-bit DAC and their equivalent average analog output voltage. 8 Here Table-3 9

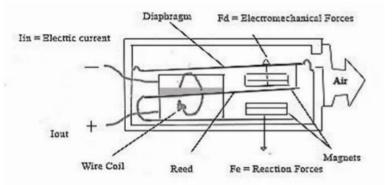

Output transducer of the hearing aid. The receiver gathers electrical signals from 10 the DAC and converts them back into acoustic energy. Balanced armature receivers (BAR) 11 12 are the preferred technology in the application of receiver by considering the efficiency (battery life) and size. It offers superior sound output and cleaner midrange sound compared 13 14 to similar-size dynamic style receivers. It provides up to 20% space savings versus similar competitive types and up to 75% versus dynamic receivers. Efficiently transforms electrical 15 energy representing the processed input signal into sound waves or acoustic energy. The 16 17 power consumed by BAR is very low eventually saving the battery life of the hearing aid.

The Balanced armature technology's transduction principle transduces the electrical signal to

acoustic signal covering even higher frequency range. BAR is cost-effective as the design is

very simple and consumes less space which helps in miniaturized the hearing aids.

Balanced Armature (BA) transducers work based on the electromagnetic principle

6 (Figure 14) and exhibit deliberately sophisticated efficiency when compared to electro-

7 dynamic transducers. The permanent magnets generate a magnetic field in which the

8 armature is balanced. When the coil is subjected to the flow of electric current a magnetic

9 flux is induced in the armature. It eventually results the end of the armature to be attracted to

10 either of the poles of the permanent magnets. The oscillations of alternating electric current

11 cause the armature to bend and moves up and down. The movement to the diaphragm is

12 initiated by the movement caused by the driver pin to which armature is connected. As the

13 diaphragm moves upwards and downwards the surrounded air molecules compresses and

14 magnifies leading to the creation of the sound wave (Dagastine, 2018). BAR receivers are

15 linear, time-invariant and stable in delivering the accurate output.

16

17

18

19 *Figure 14*. The schematic diagram of Balanced Armature transducers with diaphragm

20 controlled electromagnetically in order to generate sound.

| 1  |                                                                                                  |

|----|--------------------------------------------------------------------------------------------------|

| 2  | Conclusion                                                                                       |

| 3  | There has been much exaggeration connected with technicality behind the functioning              |

| 4  | of digital Hearing aid. This article can support the hearing health professional to unveil the   |

| 5  | technology behind working and functioning of digital hearing aid in terms of providing insight   |

| 6  | about how analog signal available in nature is converted to discrete signal and then back to the |

| 7  | analog signal.                                                                                   |

| 8  | Conflict of Interest: No conflict of interest                                                    |

| 9  | Source of Funding: None.                                                                         |

| 10 | Acknowledgment: We thank The Director and Principal of JSSISH, Mysuru, for permitting            |

| 11 | to take up this work.                                                                            |

| 12 |                                                                                                  |

| 13 | References                                                                                       |

| 14 |                                                                                                  |

| 15 | Chakraborty, P. K., Kapoor, M. R., & Pavate, K. D. (1975). Electret Condenser Microphone.        |

| 16 | J Inst Electron Telecommun Eng, 21(7), 383–385.                                                  |

| 17 | https://doi.org/10.1080/03772063.1975.11450752                                                   |

| 18 | Cheung, B. H., Acquisition, D., & Email, P. (2005). Implementation of 12-bit delta-sigma         |

| 19 | DAC with MSC12xx controller.                                                                     |

| 20 | Dagastine, G. (2018). On the cutting edge of hearing aid research. Mechanical Engineering,       |

| 21 | 140(1), 30–32.                                                                                   |

| 22 | Denhardt, D. T. (1966). A membrane-filter technique for the detection of complementary           |

| 23 | DNA. Biochemical and Biophysical Research Communications, 23(5), 641–646.                        |

| 24 | https://doi.org/10.1016/0006-291X(66)90447-5                                                     |

| 25 | John Santiago. (2020). Apply the Impulse Function to Circuit Analysis.                           |

| 26 | Keim, R. (2016). Understanding Automatic Gain Control. In All About Circuits.                    |

| 27 | Loloee, A. (2020). Understanding Delta-Sigma Modulators. 1–19.                                   |

- 1 Philippe et.al. (2020). Analogue Processing. 1–11.

- 2 Rietjens, I. M. C. M., Louisse, J., & Punt, A. (2011). Tutorial on physiologically based

- 3 kinetic modeling in molecular nutrition and food research. *Molecular Nutrition and*

- Food Research, 55(6), 941-956. https://doi.org/10.1002/mnfr.201000655

- 5 Stetzler, T., Magotra, N., Gelabert, P., Kasthuri, P., & Bangalore, S. (2008). Low power real-

- 6 time programmable DSP development platform for digital hearing aids. April, 2339–

- 7 2342 vol.4. https://doi.org/10.1109/icassp.1999.758407

- 8 Winograd, S. (1980). 5. FIR Filters. Arithmetic Complexity of Computations, 39–56.

- 9 https://doi.org/10.1137/1.9781611970364.ch5

10

# 1 Figure legends

| SL.No | Legend of the Figure                                                                                       |

|-------|------------------------------------------------------------------------------------------------------------|

| 1     | Simplified Block diagram of the architecture of digital Hearing Aid                                        |

| 2     | Waveform depicting pulse width modulation depicting the variation of input signal magnitude                |

| 3     | Working principle of the electret condenser microphone                                                     |

| 4     | Underlying architecture for an AGC system                                                                  |

| 5     | Block schematic representation of successive approximation ADC.                                            |

| 6     | The Flow Chart of successive approximation ADC.                                                            |

| 7     | Block diagram of sigma delta modulator.                                                                    |

| 8     | Technique of oversampling with an analysis in the frequency domain.                                        |

| 9     | Pictorial representation of convolution operation in Time domain                                           |

| 10    | Discrete-time index n to i in the signals x[n] and h[n] and B- C represents                                |

|       | the iteration of convolution process.                                                                      |

| 11    | Pictorial representation of y[n] obtained after convolution as per the data considered in our illustration |

| 12    | Block diagram of Sigma Delta DAC                                                                           |

| 13    | Bitstream output of Sigma Delta DAC for DIN 3011                                                           |

| 14    | The schematic diagram of Balanced Armature transducers with diaphragm                                      |

|       | controlled electromagnetically in order to generate sound.                                                 |

- 1 Table 1

- 2 The voltages are calculated and passed around within the modulator to create the resulting

- 3 bitstream

| Vin = 1 | Summing node     | Integrator V <sub>o</sub> | Comparator | DAC  |

|---------|------------------|---------------------------|------------|------|

|         | 1                | 1                         | Н          | 2.5  |

|         | 1-(2.5) = -1.5   | 1+(-1.5) = -0.5           | L          | -2.5 |

|         | 1 - (-2.5) = 3.5 | (-0.5)+3.5=3              | Н          | 2.5  |

|         | 1-(2.5) = -1.5   | 3 + (-1.5) = 1.5          | Н          | 2.5  |

|         | 1-(2.5) = -1.5   | 1.5 + (-1.5) = 0          | Н          | 2.5  |

|         | 1-(2.5) = -1.5   | 0 + (-1.5) = -1.5         | L          | -2.5 |

|         | 1 - (-2.5) = 3.5 | (-1.5)+3.5=2              | Н          | 2.5  |

|         | 1-(2.5) = -1.5   | 2+(-1.5) = 0.5            | Н          | 2.5  |

4

- 1 Table 2

- 2 Process of Convolution using the Text Table Method

- 3

|     |                       | 4                         |                                                                                                                      |                                                                                                                                    |                                                       |                                                       |                                                       |                                                      |                                                      |

|-----|-----------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|

| n<0 | 0                     | n-1                       | n-2                                                                                                                  | n-3                                                                                                                                | n-4                                                   | n-5                                                   | n-6                                                   | n-7                                                  | n>7                                                  |

| 0   | 2                     | 4                         | 6                                                                                                                    | 4                                                                                                                                  | 2                                                     | 0                                                     | 0                                                     | 0                                                    | 0                                                    |

| 0   | 3                     | -1                        | 2                                                                                                                    | 1                                                                                                                                  |                                                       |                                                       |                                                       |                                                      |                                                      |

| 0   | 6                     | 12                        | 18                                                                                                                   | 12                                                                                                                                 | 6                                                     | 0                                                     | 0                                                     | 0                                                    | 0                                                    |

|     |                       |                           |                                                                                                                      |                                                                                                                                    |                                                       |                                                       |                                                       |                                                      |                                                      |

| -   | -                     | -2                        | -4                                                                                                                   | -6                                                                                                                                 | -4                                                    | -2                                                    | 0                                                     | 0                                                    | 0                                                    |

| -   | -                     | -                         | 4                                                                                                                    | 8                                                                                                                                  | 12                                                    | 8                                                     | 4                                                     | 0                                                    | 0                                                    |

| -   | -                     | -                         | -                                                                                                                    | 2                                                                                                                                  | 4                                                     | 6                                                     | 4                                                     | 2                                                    | 0                                                    |

| 0   | 6                     | 10                        | 18                                                                                                                   | 16                                                                                                                                 | 18                                                    | 12                                                    | 8                                                     | 2                                                    | 0                                                    |

|     | 0<br>0<br>0<br>-<br>- | 0 2<br>0 3<br>0 6<br><br> | $n < 0  0  n-1 \\ 0  2  4 \\ 0  3  -1 \\ 0  6  12 \\ -  -  -2 \\ -  -  -2 \\ -  -  - \\ -  -  - \\ -  -  - \\ -  - $ | n<0 0 	 n-1 	 n-2 	 0 	 2 	 4 	 6 	 0 	 3 	 -1 	 2 	 0 	 6 	 12 	 18 	 - 	 - 	 - 	 -2 	 -4 	 - 	 - 	 - 	 4 	 - 	 - 	 - 	 4 	 - 	 - | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

# 1 Table 3 *Bitstrea*

# Bitstream and average analog output voltage for 3-bit DAC inputs

| DAC <sub>IN</sub> | DAC <sub>OUT</sub><br>BITSTREAM | ANALOG OUTPUT<br>VOLTAGE (FS = vcc)    |

|-------------------|---------------------------------|----------------------------------------|

|                   |                                 | (V)                                    |

| 0000              | 00000000                        | 0                                      |

| l <sub>001</sub>  | 00000010                        | $\frac{1}{2} X Fs$                     |

| 2010              | 00100010                        | 8 2                                    |

|                   | 01001010                        | $\frac{\overline{8}}{3} X Fs$          |

| 8011              | 01001010                        | 3<br>26 X Fs                           |

| 4 <sub>100</sub>  | 10101010                        | 26<br>26<br>4<br>8<br>X Fs<br>5<br>V F |

| 5101              | 10110110                        | 8 4 1 3                                |

| 101               | 10110110                        | $\frac{3}{8} X Fs$                     |

| 6110              | 11101110                        | 6                                      |

| _                 |                                 | $\overline{\frac{8}{7}} X Fs$          |

| 7111              | 11111110                        | $\frac{7}{8}$ X Fs                     |

| 81000             | 11111111                        | o<br>Fs                                |

| Article   | e6                           |                                  |                            |                        |        |

|-----------|------------------------------|----------------------------------|----------------------------|------------------------|--------|

| ORIGINALI | TY REPORT                    |                                  |                            |                        |        |

| SIMILARI  | 2%<br>ITY INDEX              | <b>7%</b> INTERNET SOURCES       | <b>1</b> %<br>PUBLICATIONS | <b>8%</b><br>STUDENT F | PAPERS |

| PRIMARY S | SOURCES                      |                                  |                            |                        |        |

|           | focus.ti.co                  | om                               |                            |                        | 3%     |

|           | Submitted<br>Student Paper   | I to University of               | f Southampton              |                        | 1%     |

| J         |                              | l to National Ins<br>a Surathkal | titute of Techno           | ology                  | 1%     |

| 4         | mafiadoc.<br>Internet Source | com                              |                            |                        | 1%     |

|           | www.free                     | patentsonline.co                 | om                         |                        | 1%     |

| 6         | www.ti.co                    | m                                |                            |                        | <1%    |

|           | lib.dr.iasta                 | ate.edu                          |                            |                        | <1%    |

|           | Submitted<br>Student Paper   | I to The Univers                 | ity of the South           | Pacific                | <1%    |

| 9         | Submitted                    | I to University of               | f East London              |                        |        |

<1%

| 10 | Submitted to Leiden University<br>Student Paper             | <1% |

|----|-------------------------------------------------------------|-----|

| 11 | Submitted to 8779<br>Student Paper                          | <1% |

| 12 | Submitted to University of Leeds<br>Student Paper           | <1% |

| 13 | Submitted to University of Auckland<br>Student Paper        | <1% |

| 14 | Submitted to Brigidine College St Ives                      | <1% |

| 15 | Submitted to University of Bradford<br>Student Paper        | <1% |

| 16 | Submitted to Anna University<br>Student Paper               | <1% |

| 17 | www.clear.rice.edu                                          | <1% |

| 18 | dsppc14.csie.nctu.edu.tw<br>Internet Source                 | <1% |

| 19 | Submitted to American University of Beirut<br>Student Paper | <1% |

| 20 | Whitley, Julie Anne, and Bonnie L. Rich. "A                 | <1% |

|    | Double-Blind Randomized Controlled Pilot Trial<br>Examining the Safety and Efficacy of<br>Therapeutic Touch in Premature Infants :",<br>Advances in Neonatal Care, 2008.<br>Publication |              |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 21 | Submitted to University of Macau                                                                                                                                                        | <1%          |

| 22 | ris.uni-paderborn.de                                                                                                                                                                    | <1%          |

| 23 | Submitted to University of Salford<br>Student Paper                                                                                                                                     | <1%          |

| 24 | Submitted to Sheffield Hallam University<br>Student Paper                                                                                                                               | <1%          |

| 25 | Submitted to Nanyang Technological University,<br>Singapore<br>Student Paper                                                                                                            | < <b>1</b> % |

| 26 | F. Parhizgar, Reza Asgari, Saeed H.<br>Abedinpour, M. Zareyan. "Anisotropic RKKY<br>interaction in spin-polarized graphene", Physical<br>Review B, 2013<br>Publication                  | < <b>1</b> % |

| 27 | Submitted to University of Westminster<br>Student Paper                                                                                                                                 | <1%          |

| 28 | Submitted to Taibah University<br>Student Paper                                                                                                                                         | <1%          |

| Exclude quotes       | On | Exclude matches | Off |

|----------------------|----|-----------------|-----|

| Exclude bibliography | On |                 |     |